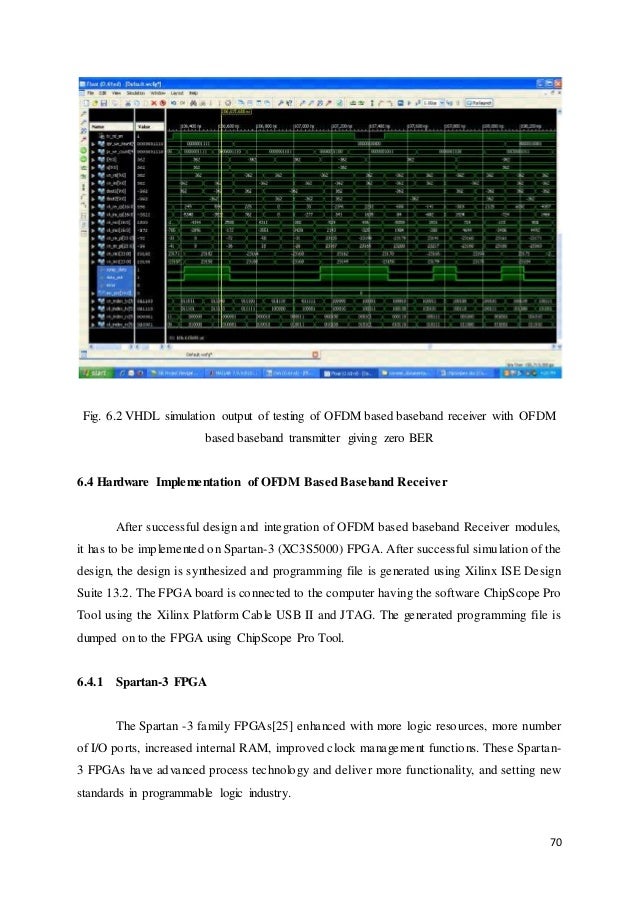

Vhdl Code For Serial Data Transmitter

Vhdl Code For Serial Data Transmitter Rating: 4,5/5 7462votes UART Transmitter and Receiver Macros 8-bit, no parity. VHDL component data data_present. Serial data transmission commences as soon as there is data in the. I’m still working on my Soft-CPU, but wanted to implement a communications channel for it to use in order to get some form of input and output from it. The easiest way to do this is to use a UART, and connect it to a USB to Serial converter for logic-level asynchronous communications. Comment Installer Tis Bmw 745 here. Knowing that I’m still pretty new to VHDL and working with FPGA systems in general at this level, I decided to develop my own UART implementation. Some may roll their eyes at this, knowing there are plenty out there, and even constructs to utilize real hardware on the Spartan 6 FPGA I’m using; but I’m a fan of learning by doing.

Serial Communications What I’m implementing is a transmitter and receiver which can operate at any baud rate, with 8 data bits, no parity and 1 stop bit. It should be able to communicate over a COM post to a PC, or to another UART. It’s working at Logic-Level voltages, which is very important – you need to use a logic level USB-Serial cable for this. Using an RS232 serial will damage things if it uses the higher voltages specified. Looking at how we transmit, the waveform looks as follows: Assuming that the ‘baud’ clock is running at the correct frequency we require, you can see that it’s fairly simple how all of this works. The idle state for the TX line is always logic high. This may seem weird, but historically the distances the wires crossed meant they were susceptible to damage, and having the idle state high meant if any problem occurred with the physical wires, you’d know about it very quickly.

To transmit an 8-bit byte, a start bit is emitted which is logic low. One ‘baud tick’ later, the least significant bit of the byte is sent, and then every baud tick follows the next bit until the most significant bit is sent.. Finally, a stop bit is sent, which is logic high.

At this point another byte can be sent immediately – or the line left idle to transmit later, after a delay. Transmitter States The transmitter is very simple. There is a data byte input, and a txSig port which is used to signal that the bits on the data output should be sent. When txSig is asserted, state moves from idle to a start state where a start bit is issued. From there, we progress to the data state, where the 8 bits of data are pushed least-significant-bit to output. Finally there is the stop bit state, before moving back to idle, or straight back to start in the case data is being streamed out. For the states, I use an integer signal as it seemed the simplest and generally the most obvious way to go about it.

Figure 11-5(a) VHDL Code for UART Transmitter library ieee; use ieee.std_logic_1164.all; entity UART_Transmitter is port(Bclk, sysclk, rst_b, TDRE, loadTDR: in std_logic. DBUS:in std_logic_vector(7 downto 0). Pinnacle Studio 9 Torrent Free Download. SetTDRE, TxD: out std_logic); end UART_Transmitter; architecture xmit of UART_Transmitter is type stateType.

The whole transmitter code is below. Tx_proc: process (tx_clk, I_reset, I_txSig, tx_state) begin -- TX runs off the TX baud clock if rising_edge(tx_clk) then if I_reset = '1' then tx_state = 2 and rx_state. I used UART to check my outputs bit-by-bit for the previous project that I did. Unfortunately, since I needed only a transmitter, the VHDL code that I have is only for the TX. I would like to settle first the answer to my question, 'What is UART?'

I found a very clear and simple discussion from the site of. UART stands for Universal Asynchronous Receiver Transmitter. It is a parallel to serial data transmitter and a serial to parallel data receiver.

The 'Asynchronous' term is there because of the fact that the clock for the UART need not be synchronized to either transmit or receive system clocks. I needed this UART to send my data outputs to my CPU's buffer and have ® check those bits.. My input ports are clock, reset, my input data (from 1 to n depending on the number of outputs that I need to read, remember number of outputs not the number of bits) and of course, my output which is just a std_logic type. The simple technique my teammate taught me is to use a counter that is triggered by a synchronous enable. For example, I need to read 4 outputs from my main block.

This 4 bit vectors will be fed to the input of my UART. Those 4-bit vectors are, say, 8 bits each. The first count of the counter (my UART) will be for the start bit, the next 8 contains the data, the last bit, the tenth bit will be the stop bit. The start and stop bits are necessary for every UART. This repeats for all my data. For every count, these bits will be fed to the 1-bit output. I show below a sample portion, taken from the middle of my code. Reform Siddur Downloads more.